≡ Передовица » Hardware » Полезное » Сигналы системной шины Агата

|

|

|---|

Сигналы системной шины Агата

Фазы работы процессора mos6502 и тактовые сигналы

Вы не задумывались, как работает системная шина Агата? Та, которая выведена на слоты? На первый взгляд тут всё просто: есть сигналы адреса, данных и r/!w. Ещё есть сигнал фазы Ф1. Для удобства ещё и сигналы выбора регистров и выбора драйвера - они появляются при обращении ЦП к регионам C0n0-C0nF и Cm00-CmFF соответственно (n равен номеру слота + 8, m - номер слота). И ещё несколько разных сигналов.

Очевидно, что устройство сложнее простой мигалки светодиодом будет иметь несколько разных исполнительных органов, некоторые из которых доступны для чтения, другие - для записи, третьи реагируют только на сам факт обращения к регистру. Для их выбора на устройстве предусматриваются несложные схемы на мелкой логике, которые пропускают сигналы шины к исполнительным устройствам с учётом заданного ЦП адреса.

Вроде всё просто. Но взгляните, например, на схему семёрочного ППИ и контроллера дисковода 840кб. В качестве исполнительных устройств и тут и там стоит кр580вв55. Но почему в схеме ППИ, в узле, синтезирующем сигнал !ЗП для вв55, используется счётчик ир16 ? А в контроллере дисковода 840кб его нет. Если изучите внимательно разные шинные интерфейсы других устройств, обнаружите много любопытного, например, ничего не делающие (на первый взгляд) элементы. Скажем, два подряд включенных инвертора.

Как же всё таки правильно подключить своё устройство к шине Агата ? Обратимся к первоисточнику: "MCS6500 microcomputer family hardware manual" (jan 1976, second edition) (C) MOS Tech, Inc.

Согласно этой книжке, 6502 имеет один вход Ф0 (пин 37) и два парафазных выхода: Ф1 (пин 3) и Ф2 (пин 39). Первоисточник никоим образом не оговаривает внутреннюю конструкцию, связывающую эти три пина. Указано лишь, что Ф1 и Ф2 будут отставать примерно на 20 нс от Ф0, причем Ф1 инвертирует Ф0 (с задержкой), а Ф2 - повторяет Ф0 (с той же задержкой).

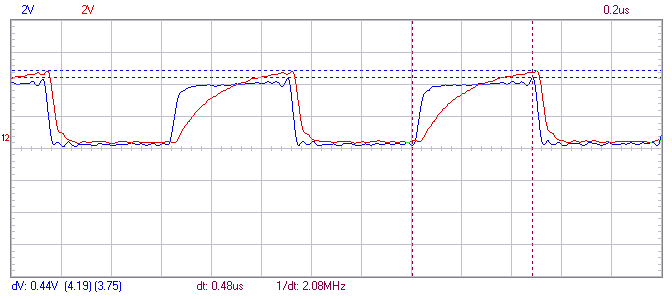

Синий - 37 (Ф0), Красный - 39 (Ф2).

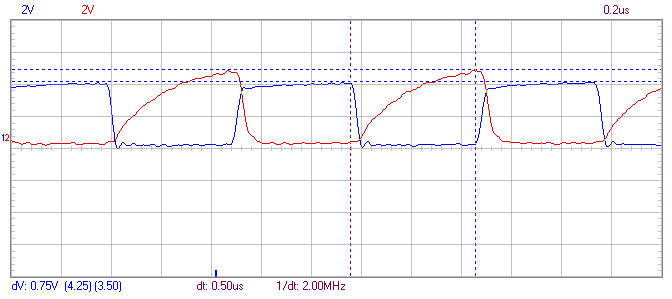

Синий - 37 (Ф0), Красный - 3 (Ф1).

Предполагалось, что на основе Ф0 и Ф1 инженер будет строить автогенератор, который в дальнейшем будет использоваться остальной системой для синхронизации ввода/вывода ЦП и периферийных устройств. Но разработчики Агата пошли совсем по другому пути.

Как известно, у Агата для синхронизации шины и устойств, подключенных к ней, используется генератор 14.3 МГц, частота которого делится на 7, получается примерно 2 МГц и на 14 - получается 1 МГц. Последний сигнал заводится на вход Ф0 ЦП. Но как ?

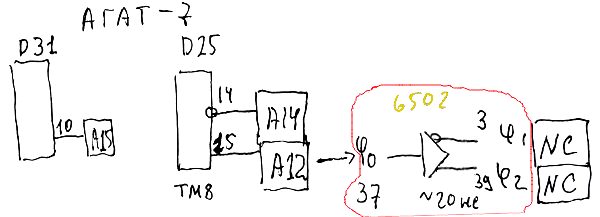

А вот по разному: тут Агат-7:

Как видно, у семёрки Ф1 и Ф2 от процессора не используется нигде и никак (Причем в мымринских схемах пин 3 проца со стороны слота вроде как подключен, а со стороны проца - вроде как не упоминается вообще. Фактического подключения нет. Так же как нет цепочки D1.4-D1.2-D1.3-D2.x). Итак:

- ламень А12 - Ф0 (с точки зрения разработчиков проца - вообще не особо нужный периферии сигнал);

- ламель А14 - незадержанный Ф1, на схемах Агата обозначен как Ф1;

- ламель А15 - 2 МГц.

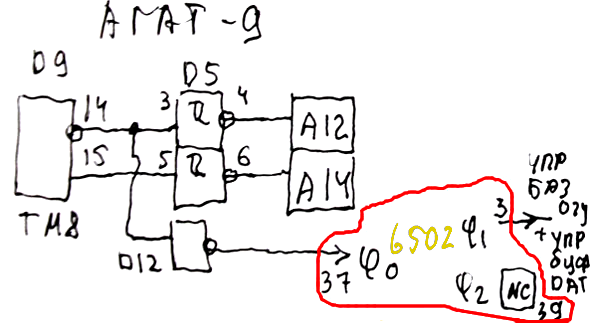

Теперь Агат9:

Схема чуть сложнее, но если допустить, что триггеры Шмидта имеют ту же задержку, что и инвертор D12, то, получается та же семёрка, только с буферизацией. Кроме того, здесь выход Ф1 (пин 3) используется в управлении базовым ОЗУ и управлении буферами ЦП.

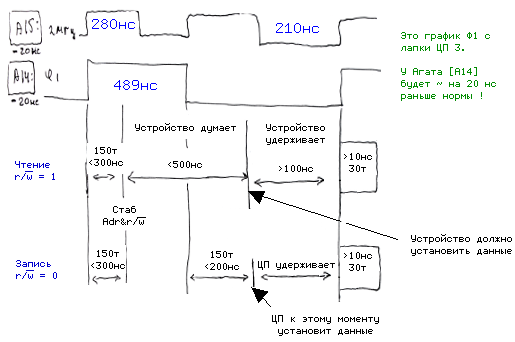

Возвращаемся к первоисточнику. Диаграмма обмена на шине:

(Буква "т" после цифр - "типичное")

Итак, А14 - это как бы Ф1, только приходящий чуть раньше чем нужно. В общем-то, ошибка перебегания здесь вряд ли составит больше 10-20 нс, в то время как характерные времена - сотни нс, так что можно считать, что всё будет нормально. Рассмотрим, как должно вести себя периферийное устройство.

Как только устройство "увидело" свой адрес на шине при Ф1 = 1, оно должно, в зависимости от сигнала r/!w, выполнить следующее:

- r/!w = 1 : у устройства есть примерно 500нс, после чего оно должно выставить данные на шину и ждать окончания очередного перехода Ф1 с 0 в 1 (затем подождать ещё 10 нс).

- r/!w = 0 : устройство ждёт перехода Ф1 с 1 в 0 и через 200нс, но не позднее перехода Ф1 с 0 в 1 (+10 нс), может считать данные с шины.

Как это реализовать ? В этом все отличия разных модулей. Про хвост в 10 нс можно забыть - это типичные задержки в распространении сигналов в Агате. С чтением всё вроде просто: достаточно собрать в кучу (адрес & r/!w !Ф1) - получится сигнал чтения. Устройство при получении этого адреса должно выставить значение на шину данных и покорно ждать своей судьбы. С записью сложнее: после !Ф1 нужно подождать хотя бы 200нс. Вот тут и начинаются различия: в ППИ, например, отсчитываются три такта частоты 14 МГц от !Ф1, после чего вв55 захватывает данные с шины. В контроллере порта принтера девятки сделано ожидание условия !Ф1 & !А15 (ламель А15 - это 2 МГц), а в контроллер 840ки опирается на !regsel, шину адреса и сигнал r/!w.

А можно ли обойтись без А15 при записи? Да, если устройство захватывает данные только по фронту сигнала записи. В этом случае (адрес & !(r/!w) & Ф1) вполне должно прокатить. Но я не пробовал :)

Кстати, вспомним про сигналы выбора регистров (А11) и выбора драйвера (Б1, Б2). Обозначим их здесь как !regsel и !drvsel (во всех схемах они обозначаются по разному). Так как эти сигналы формируются? Оказывается, как в семёрке так и в девятке они формируются уже с учётом Ф1, т.е. выставляются только при !Ф1. Это позволяет для простых устройств (использующих только два окна адресного пространства), вообще не использовать сигнал Ф1.

Таким образом: чтение = !regsel & r/!w, запись = !regsel & !(r/!w) & А15. А15, как описано выше, может быть необязательна. Конечно, не забываем, что если вы добавляете свой декодер адреса, он тоже будет вызывать ту или иную задержку.

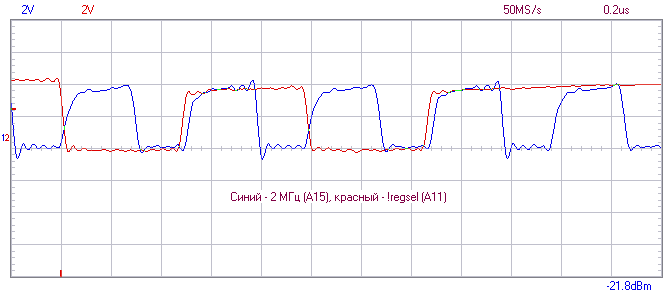

Важно 1: неидеальность сигналов. Они вроде как цифровые, но... Вот выполнение команды STA (девятка без допмодулей):

Что будет на выходе элемента И, на который будут заведены эти сигналы (!regsel & А15) ? В момент перехода А15 0->1 и !regsel 1->0 успевает проскочить короткий момент выполнения этого условия!

Важно 2: у 6502 нет никакого сигнала, указывающего на обмен данными. Т.е. считается, что каждый цикл, во время Ф1 = 0, какое-то устройство должно что нибудь прочитать или выставить с/на шину. Казус возникает в том случае, когда устройство учитывает количество чтений или записей. Дело в том, что 6502 очень запросто может выставить адрес вашего устройства не в тот момент, когда вы ожидаете. Или просто больше одного раза. Следите за руками: lda - один цикл на доступ к устройству (т.е. !regsel будет падать и подниматься один раз), sta - ДВА цикла (для индексной адресации), rol (команды типа read-modify-write) - ТРИ цикла.

Это, в частности, приводит к тому, что, в нарушение написанного в документации, порт звука (C03x) реагирует на команду записи различным образом, в зависимости от метода адресации. На самом деле, если на команды чтения реакция ожидаемая (движение мембраны из одного крайнего положения в другое), то с командами записи всё сложнее. На команду STA C030 будет обычная реакция, но на команду STA (40),Y (в ячейках 40-41 адрес C030, Y=0) будет выполнено два перемещения мембраны, следующие с очень коротким интервалом (реально, мембранна даже может "не успеть" занять первое крайнее положение). Таким образом звук получается гораздо тише, к тому же возникнут дополнительные обертона. Именно такая команда выполняется, если в сисмоне набрать команду C030:0.

Ещё больше забавных ситуаций возникает, например, при работе команд косвенной адресации, когда имеет место переход через страницы: тут можно получить обращение к вовсе незапланированному адресу, благо что в реальных прогах такое встречается редко и вряд ли зацепит ваше устройство.

Назначение контактов разъёмов системной шины

Здесь объединена информация из разных схем и описаний, как для седьмого так и для девятого Агата.

В этом тексте слово "разъём" не совпадает со словом "слот". Под "разъёмом" здесь следует понимать электромеханическое устройство соединения печатных плат, в то время как "слот" - это "разъём", имеющий собственное адресное пространство и номер в диапазоне 1-6. Такое разночтение вызвано наличием у Агат-7 разъёма X2, не имеющим собственного адресного пространства и сигналов !Device select, !ROM select. По этой причине нумерация разъёмов на плате семёрки не соответствует номерам слотов: разъём X1 - слот 1, X3 - слот 2, X4 - слот 3, X5 - слот 4, X6 - слот 5, X7 - слот 6. У девятки нумерация слотов и разъёмов совпадает (X1 - слот 1, X2 - слот 2, ...).

Почти все одноимённые пины (ламели) всех разъёмов соединены, за исключением ламелей А11, Б1, Б2 (сигналы !Device Select и !ROM Select) - они индивидуальны для каждого разъёма.

Особенности по разъёмам и архитектурам:

Задняя стенка системника X1 X3...X6 X7 - в семёрке

(вид сверху) -- X1, X3...X6 X2 - в девятке

сторона А номер пина сторона Б A Б А Б А Б

-------------------------------------------------- -------------------------------------------------------------------------

GND 30 +5v

GND 29 +5v

* 28 * Green Blue GND +5v GND +5v - нет в девятке

NC 27 NC КСИ x9.1 → x9.1 ← x9.1 - нет в девятке

*Признак машины (0->1) 26 -12v ССИ → ← - ПМ нет в семёрке

* 25 * Yrgb СГИ → NC NC ← - приоритет DMA

* 24 * NC Red → NC !БлОЗУ ← - приоритет прерываний

!NMI 23 !DMA

!IRQ 22 !RDY

!RESET 21 !Extra ROM Select

!Блокировка ПЗУ 20 NC → ↔ ← - reserved

*!Блокировка ОЗУ 19 R/nW КГИ

NC 18 A15 Address Bus 5М → ← - reserved

14 МГц 17 A14

7 МГц 16 A13

-------------------------------------------------- -------------------------------------------------------------------------

2 МГц 15 A12

f1 14 A11

!Блокировка Cxxx 13 A10

f0 12 A9

*!Device Select 11 A8

D7 Data Bus 10 A7

D6 9 A6

D5 8 A5

D4 7 A4

D3 6 A3

D2 5 A2

D1 4 A1

D0 3 A0

+12v 2 !ROM Select

+12v 1 !ROM Select

-------------------------------------------------- -------------------------------------------------------------------------

*- пины имеют очень специальное значение: различаются между 7 и 9 моделями либо между разными разъёмами.

↔ → ← - эти пины соединяются между разъёмами (при этом могут быть никуда больше не подключены).

NC - not connect. Эти линии нередко объединены между разъёмами (т.е. одноимённые ламели разъёмов соединены), но никуда больше не идут. В семёрке похожие линии (например, "!Блокировка ПЗУ") в итоге попадают на модуль процессора, но есть линии (например, А18 и Б20), которые ни для чего не используются - здесь такие линии отмечены как reserved.

Описания остальных сигналов

Тактовые сигналы изучили, теперь рассмотрим остальные сигналы. Не забывая о тактовых, конечно.

GND, +5v, +12v, -12v - питание.

Внимание на ламели А28 и Б28: на семёрке (кроме разъёма X1) они продолжают назначения ламелей А29-А30 и Б29-Б30, т.е. к ним подключены линии питания. Однако на девятке они пустые. У некоторых модулей периферии соединены ламели 28-30, у других - только 29-30. Следует быть осторожным в использовании как слота X1 семёрки (есть вероятность замыкания сигналов Green и Blue на питание некоторыми модулями) так и ламелей с номерами 28 на девятке (также есть вероятность замыкания их на питание).

A0-A15, D0-D7 - шины адреса и данных.

R/nW - указатель направления передачи данных: высокий уровень - от адресата к мастеру шины, низкий уровень - от мастера шины к адресату. Как правило, мастером шины выступает ЦП, но если он отключен от шины, мастерами могут выступать другие устройства.

f0, f1 - тактовая частота 1 МГц, привязана к фазам работы процессора.

2, 7, 14 МГц - тактовые частоты: 14 МГц - исходная, остальные - результат деления исходной.

!Блокировка ОЗУ, !Блокировка ПЗУ, !Блокировка Cxxx - низкий уровень блокирует периферийные устройства системной платы.

Блокировки ОЗУ и ПЗУ нужны дополнительным модулям памяти, которые используют общее адресное пространство с базовыми ОЗУ и ПЗУ.

Очень любопытная линия "!Блокировка Cxxx" (в том числе тем, что почти не упоминается в штатной документации): она позволяет заблокировать дешифратор региона $Cxxx на материнке. Периферийное устройство, имеющее собственный дешифратор адреса и умеющее управлять этой линией, может выполнять функции любого другого периферийного устройства, которое использует сигналы !ROM Select, !Device Select, а также дешифраторы региона $C000..$C07F. Используя этот сигнал можно построить внешний контроллер клавиатуры, пультов, таймеров и т.д., программно полностью совместимый со штатным.

Например, новый контроллер клавиатуры должен самостоятельно отслеживать линию адреса, и, обнаружив обращение ЦП в регион $C000..$C01F в фазе f0 == 0, выставить на "!Блокировка Cxxx" низкий уровень, а в фазе f0 == 1 выполнить обмен с ЦП.

Другие интересные применения этого сигнала:

- Новый контроллер пультов, позволяющий эмулировать пульты через PS/2 или USB-мышь.

- При проектировании нового видеоконтроллера, совместимого со штатным, но расчитанного на развёртку 60 Гц, может быть полезным подменять штатный таймер для того, чтобы обеспечить возможность работы программ, использующих совмещение видеорежимов (переключение режима работы ДК по таймеру с точностью до строки развёртки).

!RESET, !NMI, !IRQ - сброс и прерывания ЦП. Все сигналы имеют активный низкий уровень. Сигнал !RESET доступен только для чтения, сигналы !NMI и !IRQ - двунаправленные, периферийное устройство может управлять этими линиями или читать их. Однако при включении таймера на системной плате, линии NMI и IRQ будут управляться им, тогда периферийное устройство может только читать эти линии.

ПМ - "признак машины". Сигнал имеется только в Агат-9 и указывает на режим работы контроллера базового ОЗУ. Высокий уровень - режим "Агат", низкий уровень - режим "Apple". Сигнал переключается в низкий уровень записью по адресам $C0Fx, обратное переключение возможно только через обесточивание компьютера. Этот сигнал используется модулями расширения ОЗУ.

В семёрке ламель ПМ считается неиспользуемой, но ячейка 121 требует подключения к этой ламели сигнала от дешифратора адреса (6 нога микросхемы D7 - К555ИД4). Этот сигнал указывает на обращение к региону адресов $C05x - это адреса управления эпловским видеоконтроллером (а, по совместительству, и отключение таймера в семёрке).

!Device select, !ROM select, !Extra ROM select - признак обращения к регионам портов ввода-вывода.

Все сигналы имеют активный низкий уровень. Эти сигналы поступают в фазе f0 == 1 от дешифратора адреса.

!Extra ROM select активен при обращении к адресам $C800..$CFFF.

!ROM select активен при обращении к адресам $CnXX, где n - номер слота, X - любая цифра.

!Device select активен при обращении к адресам $C0iX, где i = n + 8, n - номер слота, X - любая цифра.

!DMA, !RDY. !DMA - отключение ЦП от шин адреса, данных и сигнала R/nW. !RDY - остановка ЦП. Активные уровни - низкие.

Эти сигналы позволяют устройству поиграть в мастера шины. Неспеша изучить чем занят процессор, а также отключить его от шины совсем и порулить любой периферией самостоятельно.

Остановка процессора разрешена в моменты чтения данных (f0 & R/nW == High). Вновь разрешить работу процессора нужно в начале фазы f0 таким образом, чтобы линия !DMA позволила периферийным устройствам сформировать запрашиваемые в данном цикле данные (сперва разрешить !DMA в f0 - Low, затем !RDY в f0 - High).

x9.1 в семёрке выходит на разъём "Видеосигнал". Эта линия использовалась ячейкой 121 для вывода монохромного видео. В некоторых версиях ячейки 121 детали для этой линии отсутствуют. Также на материнке эта линия может быть обрезана.

Линии "приоритет DMA" и "приоритет прерываний" нужны для того, чтобы соседние устройства могли выстраивать иерархию в управлении разделяемыми рессурсами. Они соединяются не параллельно, но последовательно (например: X3.А25 подключена к X4.Б25, X3.А24 подключена к X4.Б24). Документация не указывает, какие именно прерывания имеется ввиду (NMI или IRQ). Фактически, линия А24 на крайних разъёмах (X7 в семёрке и X2 в девятке) блокирует основное ОЗУ, т.е. используется для выстраивания иерархии модулей расширения памяти. В то же время линия !Блокировка ОЗУ также подводится ко всем разъёмам (кроме X1 семёрки) на ламель А19, но её использует только ячейка 121.

Модули ДопОЗУ используют эти линии следующим образом:

- На семёрке модули читают Б25 (причем тут есть ошибка: нет подтягивающего резистора на модулях, а входы 559ип2 довольно чувствительны!) и блокируются им, признак блокировки уходит на А25. Если же блокировки нет, но есть обращение (выставлен в "1" бит D3 в регистре управления модулем), то модуль выставляет признак активности на А25. Также, при обращении к адресам $8000..$FFFF (фактически, модули работают только в этом диапазоне) и активности модуля, модуль может блокировать базовое ОЗУ через линию А24. Это требуется только в случае, если объём базового ОЗУ превышает 32 Кб (чего не случалось в серийных машинах). Для того, чтобы это работало, нужна перемычка в линейке конфигурационных джамперов (впаивалась в версии модуля "ДопОЗУ"), а модуль ДопОЗУ должен быть установлен в разъём X7. Если модулей несколько, они устанавливаются от разъёма X7 вниз (X7, X6, X5...). Все сигналы управления - прямые, активные уровни - высокие.

- На девятке используется только две линии: Б24 - вход внешней блокировки модуля (более высокого ранга), а А24 - выход блокировки базового ОЗУ (и нижестоящих модулей). А24 подключен к линии блокировки базового ОЗУ только на разъёме X2, поэтому первый модуль ДопОЗУ устанавливается в X2. Если модулей несколько, они устанавливаются от разъёма X2 вверх (X2, X3, X4...). Оба сигнала управления - инверсные, активные уровни - низкие.

Важно: многие линии могут быть управляемы с любого из разъёмов. Если ни одного управляющего устройства нет, резисторы на системной плате будут подтягивать линии к неактивным уровням. Однако величины этих резисторов довольно высоки и если линией требуется управлять быстро (в пределах одного периода f0) нужно либо использовать полноценный push-pull или 3-state выход (не ОК). Также каким-то образом нужно предусмотреть ситуацию, в которой несколько устройств попытаются одновременно управлять линией. Здесь есть два варианта: либо использовать свободные ламели для передачи информации о приоритете того или иного устройства, либо использовать 3-state выход, который будет активен только у одного устройства в одно время (например, на основании состояния шины адреса и/или R/nW), причем, перед освобождением линии, устройство должно самостоятельно вернуть линию в неактивное состояние (нельзя расчитывать на то, что подтягивающий резистор сможет быстро перезарядить паразитные ёмкости).

Подробнее об особенностях некоторых разъёмов

X1

Назначение X1 в семёрке однозначно не известно. На него выводятся многие сигналы ДК, что позволяет устройству, установленному в разъём, выводить картинку, синтезируемую ДК. В то же время к X1 не подводились некоторые сигналы, например, цепочки приоритетов DMA и прерываний.

Предположительно, этот разъём использовался для Secam-кодера, позволявшего подключить к Агату, в качестве монитора, любой телевизор. Разумеется, с некоторой потерей качества картинки. Возможно, это предназначалось для больших демонстрационных телевизоров. Другое предположение: некоторые версии ячейки 121 (плата дополнительного видеоконтроллера, программно совместимого с видеоконтроллером Apple ][) могли быть реализованы для этого разъёма. Это бы позволяло им выводить на разъём видеосигнала как собственный сигнал, так и сигнал, синтезируемый на материнской плате. С сожалению, имеющиеся в нашей коллекции ячейки 121 не имеют такой возможности и устанавливаются в разъёмы X3..X7 (в разъёмы X1 их устанавливать не рекомендуется, так как у ячейки замкнуты пины А28-А30, таким образом она будет шунтировать зелёный канал на разъёме RGB материнской платы).

Дополнительные сигналы разъёма:

- 5М - меандр частотой 5.25 МГц. Является опорным сигналом видеосистемы.

- СГИ, ССИ - строчный гасящий и синхронизующий импульсы.

- КГИ, КСИ - кадровый гасящий и синхронизующий импульсы.

- Red, Blue, Green, Yrgb - сигналы включения и яркости цветовых каналов.

Все импульсы имеют высокий активный уровень. Гасящие импульсы начинаются раньше синхронизующих и имеют длительность в 3-5 раз больше.

Кроме прочего, сюда подводятся сигналы !Device select и !ROM select, соответствующие слоту "1", так что для некоторых устройств этот разъём вполне может использоваться наравне с другими.

На некоторых платах семёрки этот разъём не устанавливался, хотя разводка платы его предусматривает.

В девятке сигнал !ROM Select разъёма X1 используется контроллером базовой памяти, что также частично сокращает возможности этого разъёма, однако в остальных отношениях X1 ничем не отличается от других разъёмов. Этот сигнал, тем не менее, выведен на разъём, поэтому устройство может его анализировать и даже захватывать операции записи по соответстующим адресам. Но оно не должно отвечать на запросы чтения. Некоторые контроллеры специально изготавливались для работы в этом разъёме, например, контроллер "мыши" фирмы Nippel - инструкция прямо рекомендовала использовать X1, чтобы не занимать "полноценные" разъёмы.

X2, X7

X2 в девятке, так же как и X7 в семёрке, имеет входы сигнала блокировки базового ОЗУ. Таким образом, в этот разъём можно устанавливать модули ДопОЗУ, перекрывающее базовое ОЗУ. Если таких модулей требуется использовать несколько штук, то следующие модули нужно устанавливать в X3, X4...(в девятке) или X6, X5... (в семёрке) - в этом случае они выстраивают схему приоритета и используют линию блокировки базового ОЗУ по цепочке совместно.

Разъём процессора X2 в семёрке почти полностью повторяет разъёмы X3..X7 за одним исключением:

он как бы не имеет своего адреса и выпадает из общей нумерации слотов. Отличается

только в следующих контактах:

А11 - здесь используется для передачи сигнала обращения процессора к региону $C000..C7FF.

Этот сигнал используется дешифраторами адресов периферии и может быть заблокирован любым другим

устройством через линию А13.

Б1,2 - никуда не подключены.

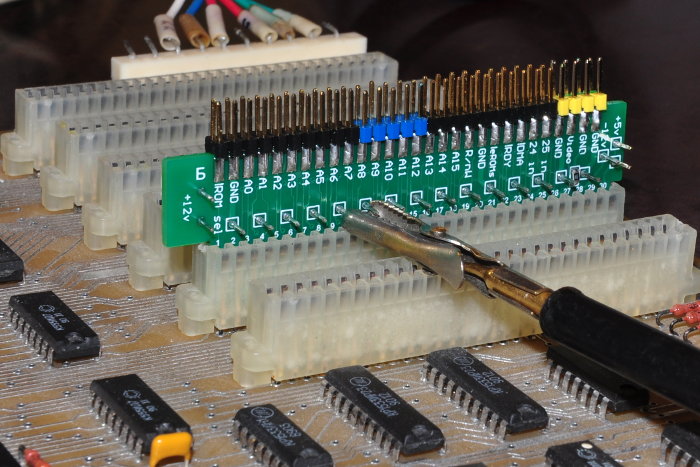

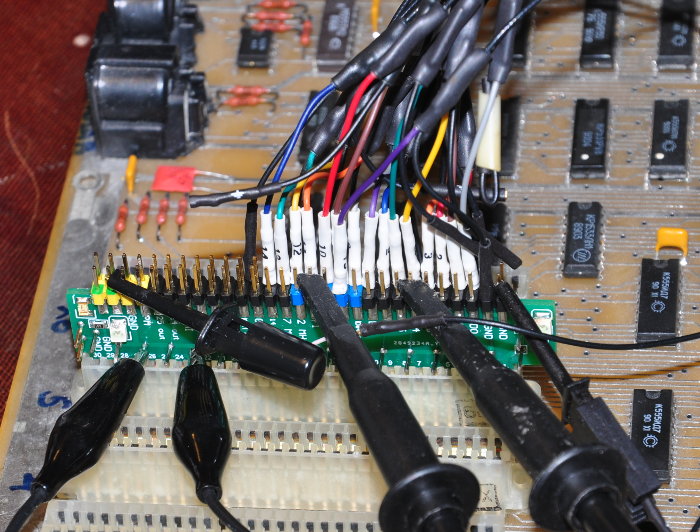

Плата с коннекторами, позволяет удобно подключить различные виды щупов измерительной техники к шине Агата. Плата не имеет активных элементов и позволяет подключать как логический анализатор, так и осцилограф или вольтметр. Также здесь размещены три светодиода, подключенных на линии питания +5в, +12в и -12в.

* * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * *