Навигационная цепочка "где я сейчас?" - траектория от главной до текущей страницы сайта. Breadcrumbs.

Передовица (меню разделов)

⇓

Hardware

⇓

ДЗУ (дисководы и их контроллеры)

⇓

Исследование КНГМД 840

⇓

Общий обзор

Общий обзор

Условно можно разделить контроллер на следующие блоки:

- Декодер адреса: формирует сигналы выбора отдельных блоков контроллера на основании сигналов R/!W, !IOSel, !ROMSel и младших бит адресной шины. Сюда же можно отнести шинный формирователь.

- ПЗУ драйвера: понятно. Даже не будем изучать её включение.

- Умножитель частоты: контроллеру нужна частота 4 МГц, она получается умножением на 2 частоты 2.04 МГц, получаемого с системной шины.

- Выходные буфера: усиливают сигналы, отправляемые дисководу. Сюда же можно отнести формировать сигнала Step- движения головки и сигналов выбора привода.

- Интеллектуальные регистры-защёлки. Они хранят слова состояния, режимов, данные записи и чтения.

- Секвенсор и канал кодирования/декодирования данных.

Все блоки, кроме секвенсора, весьма просты и будут рассмотрены на этой странице. А вот секвенсор - крайне хитрая железка, ему будут посвящены отдельные страницы.

ВАЖНО: текст этой страницы писался до того, как я встретился с официальными схемами, поэтому маркировка микросхем была моя собственная. Так как сейчас схемы есть, текст был дополнен маркировками из официальной схемы. Первым числом идёт моя маркировка, затем знак "/" и вторым числом - официальная, второй версии. Маркировка микросхем, упоминаемых в официальной документации по программированию, была известна мне заранее: D1, D6, D25, D14, D15 - эти номера совпадают везде, кроме первой версии.

Декодер адреса и буфер системой шины

Сформирован элементами D2/11, D3/2, D4/3, D5/4, D6'/5, D8/7.

D2/11 (двунаправленный канальный усилитель): с одной стороны у него подключается системная шина данных, с другой - выходы ПЗУ D1 и параллельно включенные магистрали регистров D14, D15.

На остальных элементах собран декодер, выходные сигналы которого подключаются к элементам D14, D15 на входы выбора адреса и операции (!запись, !чтение). Регистры D14, D15 активизируются при обращении к младшим 8 адресам управления (C0x0..C0x7). Кроме того, вывод 11 кристалла D5/4 идёт на D8/7, который активируется для старших 8 адресов управления (C0x8..C0xF) и выдаёт сигналы, вызывающие запись синхросбоя (C0x8), сдвиг головки (C0x9) и сброс флага сбоя синхронизации (C0xA).

Первый элемент микросхемы D3/2 просто инвертирует общесистемный сигнал сброса для передачи на микросхемы D14, D15.

Умножитель частоты

Этот блок различается во второй и третьей версиях.

Третья версия

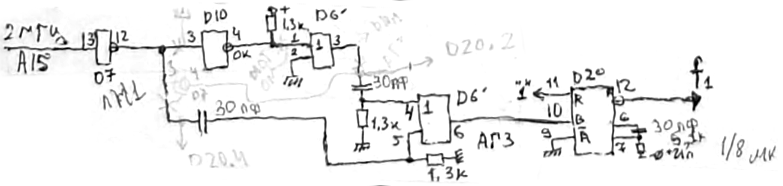

Так как официальных схем третьей версии у меня пока нет, здесь я использую только свою нумерацию микросхем.

Умножитель образован элементами D6', D7, D10, D20. Действует следующим образом: на каждую смену сигнала 2 МГц RC-цепочками формируется короткий импульс (т.е. короткий импульс при спаде 2 МГц и при подъёме). В дальнейшем эти импульсы растягиваются до 1/8 мкс элементом D20. Карандашом поверх набросан вариант второй версии.

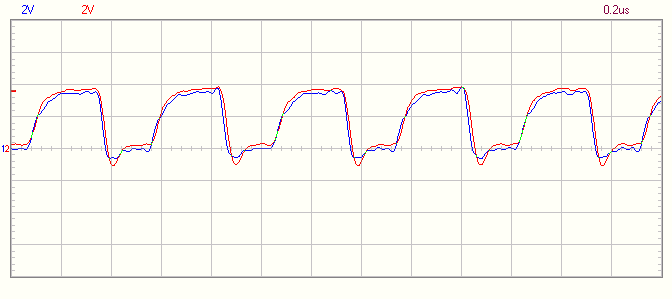

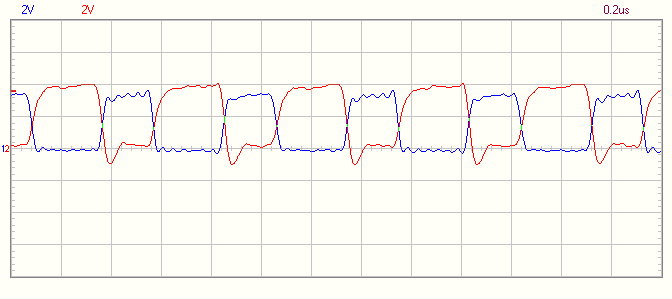

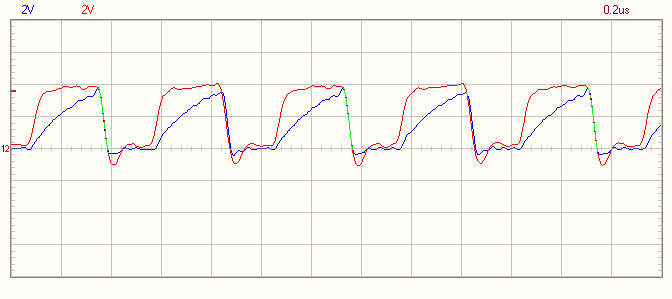

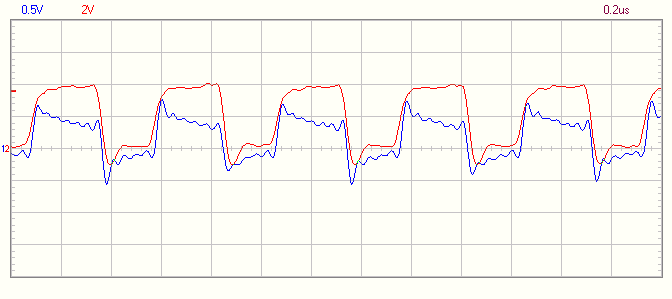

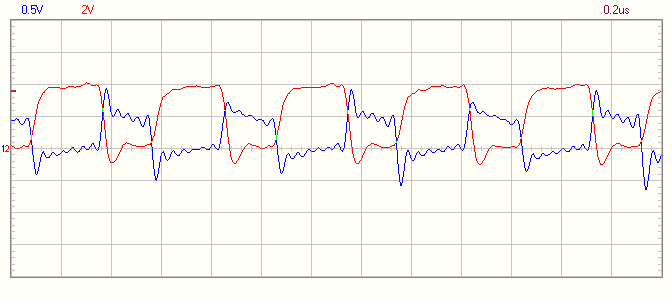

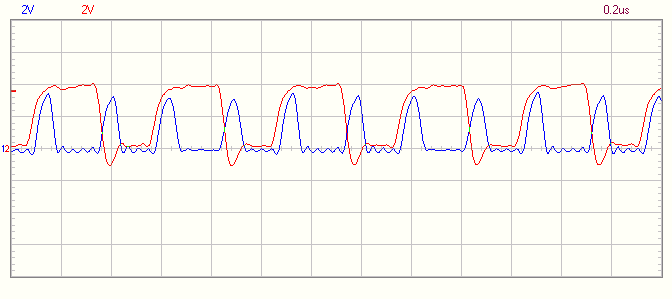

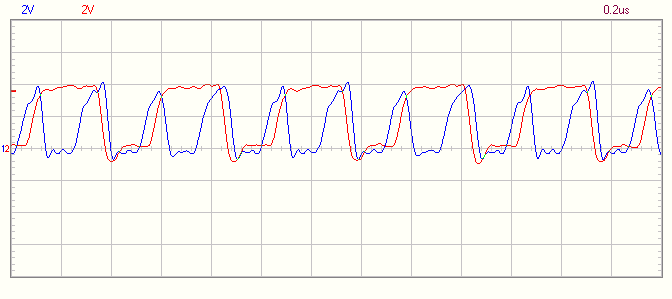

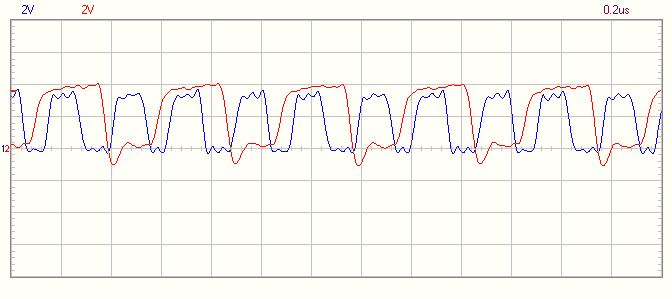

Для третьей версии я снял осцилограммы. Здесь красный - сигнал синхронизации 2.04 МГц, синий - описываемый сигнал.

Входной сигнал 2.04 МГц на входе 13 м/с D7.

С выхода 12 этой м/с снимается инвертированный сигнал.

Инвертор D10 с открытым коллектором на выходе 4 немного искажает сигнал при инвертировании..

Сигнал на входе 4 м/с D6'.

Сигнал на входе 5 м/с D6'.

Выход 6 м/с D6'.

С выхода 12 м/с D20 снимается уже почти прямоугольный, со скважностью 1:1, сигнал синхронизации 4 МГц.

Для некоторых частей контроллера нужен этот же сигнал, но в инверсном виде. Он снимается с вывода 6 м/с D7.

Вторая версия

Здесь нумерация микросхем по официальной схеме версии два.

Логика работы, по видимому, совпадает с третьей версией. Только в качестве формирователя коротких импульсов используется первая половина D18 и D16.3. После чего короткие импульсы растягиваются второй половиной D18.

Выходные буфера

D12/24, D13/12 - магистральные усилители. Просто усиливают сигналы перед передачей в канал. Но сюда же можно отнести и одновибратор, образованный микросхемой D9/10: по входу 9 она получает короткий импульс при обращении к адресу C0x9 и растягивает примерно до 1.5 мкс. Ещё один одновибратор: D11/20, вероятно, он предназначен для того, чтобы поддерживать работу дисковода в течение некоторого времени после программной остановки. Это позволяет заканчивать чтение сектора командой выключения дисковода и начинать следующий сектор командой включения - если интервал будет небольшим, двигатель не будет останавливаться.

Однако эта техника будет работать не всегда: некоторые драйвера при ошибке чтения выполняют "распрограммирование" регистров D14, D15, в этом случае сигнал выбора переключается на второй привод и, несмотря на работу D11/20, сигнал с первого привода снимается сразу. Это не приводит к ошибкам в работе, но выглядит немного непривычно.

Ещё одна особенность: формирователь сигнала выбора привода: в основном, это м/с D12/D24. Её вывод 3 подключен к разъёму шлейфа дисковода, на лапку A1. В штатном кабеле этот контакт не задействован, сигнал на нём будет появлятся при обращении к любому из приводов. Возможно, планировалось на него повесить светодиод индикации включения дисководов.

Интеллектуальные регистры-защёлки

Не знаю как ещё назвать эти микросхемы: D14, D15. Каждая из них имеет три восьмиразрядных регистра, каждый из которых может хранить и выводить данные, переданные от ЦПУ либо вводить данные по запросу в ЦПУ. Причем D14 стандартным драйвером программируется так: порты A, B - ввод, C - вывод. А вот D15 переводится в режим аппаратного стробирования и раскладка становится такой: A - вывод со стробированием, B - ввод со стробированием, сигналы управления в C. При этом часть C формируется самой микросхемой, а часть вводится извне напрямую.

D14 управляет различными "тупыми" функциями, как -то "включить", "выключить", "привод", "сторона", "направление", "index", "трек 0", "готовность", "защита записи" и т.д. - т.е. выполняет функции, напоминающие PC-шный LPT-порт - просто передаёт от дисковода процессору, а от процессора - дисководу медленно и редко меняющиеся биты.

D15 действует значительно сложнее: она передаёт только данные для записи/чтения, причём для канала чтения передаёт только сигнал готовности от декодера к ЦПУ (нет смысла передавать готовность от ЦПУ к декодеру - он же не может тормознуть диск с точностью до бита, если процессор не готов), а для записи - от ЦПУ к декодеру (по той же причине).

Часть микросхемы D6'/16 тоже можно отнести к этому блоку: по входам 9 и 10 она получает сигналы готовности регистров данных чтения или записи от D15 (вообще-то они предназначены для генерации прерывания процессора, но в этой схеме использованы по другому) и выставляет их в разряд C7 той же D15, откуда их в режиме программного пуллинга считывает драйвер.

На следующих страницах мы рассмотрим работу автомата кодирования/декодирования данных. Он связан с остальной схемой только через D15, для чего используются её восьмибитные порты A и B, а также два бита порта C номер 2 и 4. Оба бита поступают с одной линии автомата и, в зависимости от режима работы контроллера (чтение/запись):

- Чтение: указывают на готовность очередного прочитанного байта (D15 захватывает его из автомата и хранит до считывания драйвером).

- Запись: указывают на готовность сдвигового регистра к принятию очередного байта для записи (D15 при этом выставляет у себя флаг "регистр свободен", драйвер может передать ей очередной байт).