Навигационная цепочка "где я сейчас?" - траектория от главной до текущей страницы сайта. Breadcrumbs.

Передовица (меню разделов)

⇓

Hardware

⇓

ДЗУ (дисководы и их контроллеры)

⇓

Исследование КНГМД 840

⇓

Секвенсор и канал обработки данных

Секвенсор и канал обработки данных

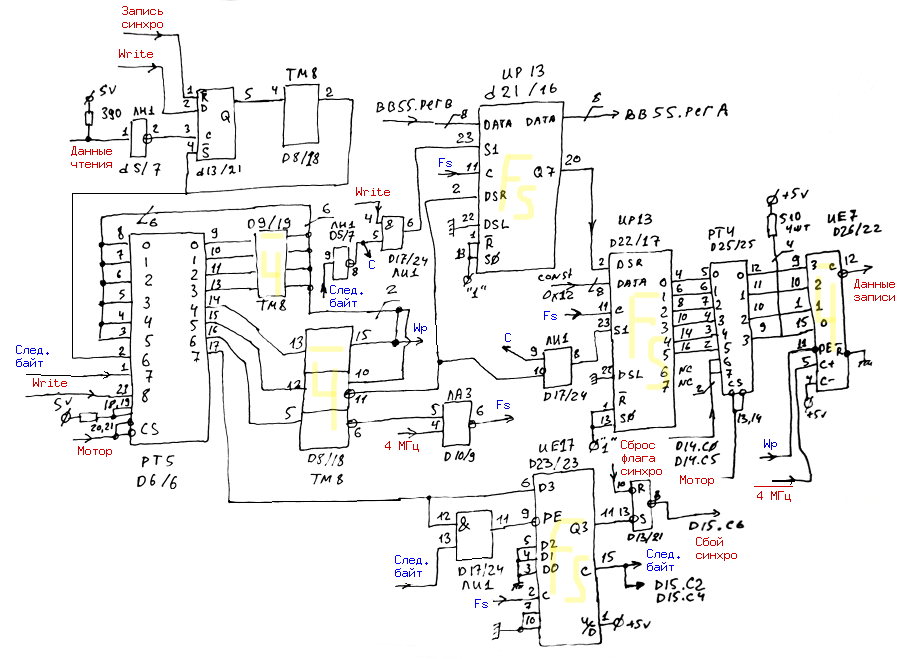

Я перерисовал этот кусок схемы, чтобы нагляднее показать структуру. Нумерация микросхем двойная: первым идёт номер из второй официальной версии, вторым - номер в моём старом полном варианте схемы. Красным цветом обозначены связи с остальной частью схемы, синим - внутренние связи, используемые только внутри этого участка. В тексте маркировка микрух - только по официальной схеме.

Секвенсор

Он образован микросхемой ПЗУ D6 и группой защёлок D8, D9. Защёлки тактируются инвертированным сигналом 4 МГц.

Шесть младших выходных бит ПЗУ проходят защёлки и возвращаются на младшие адресные входы ПЗУ. Таким образом, все программы делятся на 64 шага, по которым исполнение может перемещаться даже при неизменных входных сигналах. Это особенно хорошо будет видно на программе чтения. Причем младшие четыре бита адреса нигде не используются, иначе как для выбора шага программы. А вот биты D4 и D5 используются для управления внешними устройствами: таким образом, секвенсор выдаёт команды не только отдельными командными разрядами, но и самим номером шага программы. В 140-ке это использовалось только для формирования сигналов записи, здесь же всё сложнее.

Помимо бит, указывающих на шаг программы, на адресный вход ПЗУ подаются следующие сигналы: A6 - данные, прочитанные с дискеты (в режиме Чтение) или команда записи синхросбоя (в режиме Записи). A7 - сигнал "следующий байт", он будет описан в разделе, посвященном счётчику бит. A8 - выбор режима Запись или Чтение. Этот бит самый простой: он делит адресное пространство ПЗУ на две программы, исполняющиеся в соответствующих режимах работы контроллера.

Выходные биты D6 и D7 используются только для управления внешними устройствами. Бит D6, совместно с сигналом 4 МГц (не инвертированным!), образуют сигнал Fs. Это сигнал указывает, что программа секвенсора обработала очередной бит и сдвиговые регистры и счётчик бит должны что-то предпринять. Что именно - зависит от других сигналов. Бит D7 задаёт режим переключения счётчика бит D23.

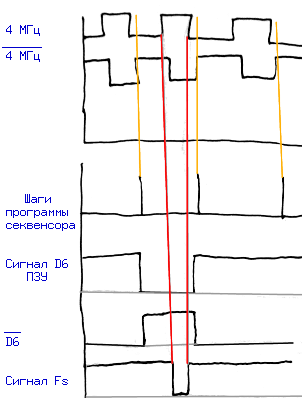

Внимательно рассмотрим фазировку сигнала Fs:

Исходный сигнал 4 МГц. Этот сигнал инвертируется, инверсия немного отстаёт от оригинала. По её положительному фронту тактируется секвенсор (D8, D9) и выходной счётчик кодера данных (D26). Секвенсор выставляет управляющие сигналы и адреса следующего шага через защёлку D8 (например, на выводах D8.11, D8.15). С вывода D6.16 сигнал поступает на D8.5, при поступлении очередного тактового импульса этот сигнал выводится на D8.6 и оттуда попадает на D10.5. До этого момента сигнал изменяется одновременно с D8.11 и D8.15 (на рисунке обозначен как D6). Но в D10 происходит конъюнкция с сигналом 4 МГц (с которого всё начиналось) и, в результате, фронты получившегося сигнала Fs оказываются "внутри" остальных сигналов секвенсора. Т.е. Fs "щёлкает" после установления всех состояний секвенсора, незадолго до очередного его переключения. Это важно, так как все исполнительные устройства, тактируемые Fs, реагируют именно на его передний фронт. Этот фронт должен пройти до того, как секвенсор начнёт изменять своё состояние (в том числе потому, что его очередной шаг зависит от состояния исполнительных устройств).

Счётчик обработанных бит

Счётчик D23 считает вверх, но помимо выполнения инкремента он может устанавливаться в значения 8 и 0. Всё происходит по командам секвенсора. Счётчик имеет двойное назначение: счёт бит байта и элемент цепочки передачи сигнала "синхросбой". Сейчас попробуем разобраться в этом, довольно оригинальном, узле.

Секвенсор, выполняя чтение, должен отслеживать сбои потоке входных данных - синхросбои. В случае синхросбоя секвенсор настраивает фазу приёма данных, а также должен сбросить счётчик бит и сообщить драйверу о произошедшем синхросбое.

В обычном состоянии на выходах D6.17 (сигнал D7) и D23.15 ("перенос") присутствует единица. Следовательно, единица же будет на выходе D17.11 и на входе D23.9 ("параллельная загрузка"). В этом случае счётчик D23 по каждому Fs увеличивает значение на единицу - это обычный подсчёт обработанных бит.

Когда счётчик D23 доходит до значения 15, на его выходе "перенос" (D23.15) появляется ноль. Таким образом и на его входе "параллельная загрузка" тоже появляется ноль и на следующий такт в счётчик загружается число 8. Так как выход "перенос" является для остальной схемы сигналом для перехода к следующему байту, в этот момент происходит обмен байтами между регистрами 580вв55 и D21 (а также, в режиме записи, секвенсор может задержать работу на несколько мкс, чтобы сформировать синхросбой).

Если же при чтении секвенсор обнаруживает синхросбой, он выставляет на D6.17 ноль и, таким образом, на входах D23.6 (старший разряд при параллельной загрузке счётчика) и D23.9 ("параллельная загрузка") также появляются нули. Это приводит к тому, что на следующем такте Fs в счётчик будет загружено значение 0. При этом триггер D13, вход !S которого подключен к D23.11 (выход старшего разряду счётчика), переходит в состояние "1". Эту единицу драйвер может прочитать в регистре C микросхемы D15 (580вв55).

Причем важно то, что так как счётчик перешел к значению 0, триггер D13 будет удерживаться в состоянии "1" по крайней мере следующие 8 принятых бит, пока счётчик не дойдет до значения 8 (т.е. не начнёт принимать второй байт после синхросбоя). Это будет происходить даже если драйвер попробует сбросить флаг синхросбоя (т.е. триггер D13). Также нужно заметить, что сигнал "конец байта" тоже не будет синтезироваться для первого, после синхросбоя, байта. Таким образом, этот байт не доступен драйверу.

Что интересного в этом узле ? Если забыть о его конструкции и попробовать создать заного, логичным кажется сигнал D6.7 вывести сразу на вход !S триггера D13 (драйвер сможет увидеть произошедший синхросбой) и этот же сигнал завести на сброс некоего трехбитного счётчика (начало байта). Вроде как избавимся от элемента D17 и схема понятнее станет. Но тут есть заковыка: используемый счётчик должен иметь вход сброса (причём, если не менять программу секвенсора - синхронный), ровно 3 разряда и выход сигнала переноса, действующий во время последнего, 7 бита. Но вот такого готового счётчика я не помню. А чтобы его сделать на основе существующих счётчиков (обвешивая другими элементами) потребуется заметно больше единственного двухвходового элемента И. Так что решение Филиппова выглядит весьма изящно.

Формирователь данных чтения

Входной сигнал от дисковода проходит группу элементов D5, D13, D8. С первым всё понятно - он только восстанавливает форму сигнала. Интереснее второй и третий. Это формирователь сигнала чтения, точно такой же как в 140-ке. Его задача: преобразовать любой импульс, пришедший от дисковода, в импульс заданной длительности, равной одному шагу секвенсора. Разбирая программу чтения, будет видно, почему это важно.

Как это работает: сигнал Write = 0, он приходит на вход D триггера D13. На каждый переход уровня 0 -> 1 на входе C триггера D13 на выходе Q будет появляться (и фиксироваться там) нолик. Но только к очередному тактовому сигналу !4 МГц этот нолик пройдёт и зафиксируется на выходе D8.2. Когда это произойдёт, нолик попадёт на вход D13.4 !S и триггер D13 сразу вернётся в состояние единицы. Даже если сигнал на входе C будет оставаться единицей, триггер D13 не будет на это реагировать до следующего перехода сигнала C из нуля в единицу.

Однако в режиме записи Write = 1 и любой импульс будет пытаться перевести триггер в единичное состояние (в котором он и так, скорее всего, находится). А вот сигнал "запись синхросбоя", формируемый драйвером, перебросит триггер в нулевое состояние. И путь прохождения этого нуля будет тот же самый: D13.5 - D8.4 - D8.2 - D13.4 - секвенсор получит имульс длительностью один свой шаг... Кажется. Не, не совсем так. Дело в том, что секвенсор работает заметно быстрее центрального процессора и сигнал "запись синхросбоя" длится около двух шагов секвенсора. Поэтому на D8.2 формируется нечто вроде 11111010111111 - два нуля, разделённые единицей. Но программа секвенсора построена так, что это не мешает её работе.

И вновь - согласитесь - это весьма красивое решение. На вход секвенсора нужно было подать как сигнал чтения, так и сигнал "запись синхросбоя". При этом сигнал чтения нужно было выровнять по длительности. На узле из двух элементов удалось сделать и это и ещё "бесплатно" сделать подмешивание "записи синхросбоя" !

Регистр накопления и расхода байта

Микросхема D21 используется как в режиме чтения, так и в режиме записи. Её роль весьма проста - это аккумулятор данных. В режиме чтения она получает очередной бит данных и команду "сдвинуть байт". После приёма полного байта счётчик бит выдаёт сигнал "следующий байт". По этому сигналу 580вв55 захватывает байт из регистра D21.

В режиме записи всё немного сложнее: 580вв55 держит очередной выставленный для записи байт на своих выводах. D21 срабатывает по сигналу Fs, но, благодаря элементам D5/D17, при появлении сигнала "следующий байт" происходит параллельная загрузка байта, выставленного 580вв55. Если сигнал "следующий байт" отсутствует, то выполняется сдвиг байта. Очередной бит будет с выхода D21.20 захвачен входом D22.2 и, таким образом, попадёт в конвейер MFM-кодера.

Обратите внимание: у этой микры довольно хитрая нумерация сигналов. Вход 2 помечен как DSR (Data Shift Right), но, с точки зрения включения в схему, сдвиг происходит влево! Скорее всего, этот фокус произошел при неправильном копировании импортной документации: там разряды этого регистра обозначены как A B C D E F G H, при этом A - самый левый. Вероятно, в отечественных справочниках решили исправить такое безобразие и, как положено, пронумеровать биты. Но протупили с тем, что A - хотя и первая буква алфавита, но должна соответствовать D7, а не D0.

Автомат кодирования и предкомпенсации записи

Пожалуй, этот блок удивил меня больше всего. Всего на трёх логических микросхемах (D22, D25, D26) построен полный автомат кодирования и предкомпенсации записи. Разве что он требует тактирования от секвенсора. Если бы не было необходимости формировать синхросбой, он мог бы работать и без секвенсора, довольно было бы подвести тактовую частоту. Однако устройство и работа этого автомата непросты и поэтому им посвящен отдельный раздел.