Навигационная цепочка "где я сейчас?" - траектория от главной до текущей страницы сайта. Breadcrumbs.

Передовица (меню разделов)

⇓

Hardware

⇓

Сеть

⇓

Контроллер сети (НИИВК)

Контроллер сети (НИИВК)

Штатная сетевая карта из комплекта КУВТ-АГАТ.

Авторы: Е.Н.Глыбин, С.В.Козаренко, К.М.Левин. НИИВК 1988-90 год.

Разыскивается! Если вы автор или что-то знаете о нём, свяжитесь с нами!

(ЗАЧЕМ ЭТО?)

Сделана она была вполне солидно. Есть микросхема ПЗУ, т.е. у неё был и onboard-драйвер и BOOT-ROM. Это уже был не просто порт для близлежащего устройства, а полноценный интерфейс дальней связи (сотни метров).

EPROM экспериментальной и серийной версий.

EPROM экспериментальной и серийной версий.

Плата поставлялась с ИКП ОС Локальной Сети.

* * *

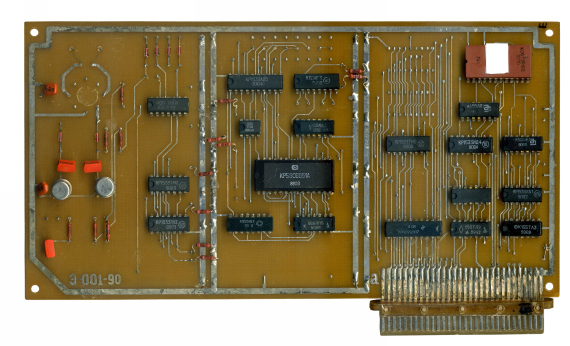

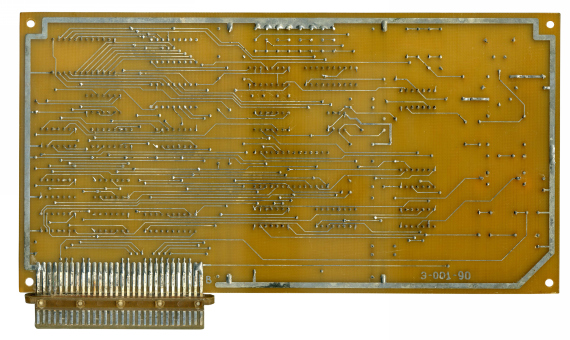

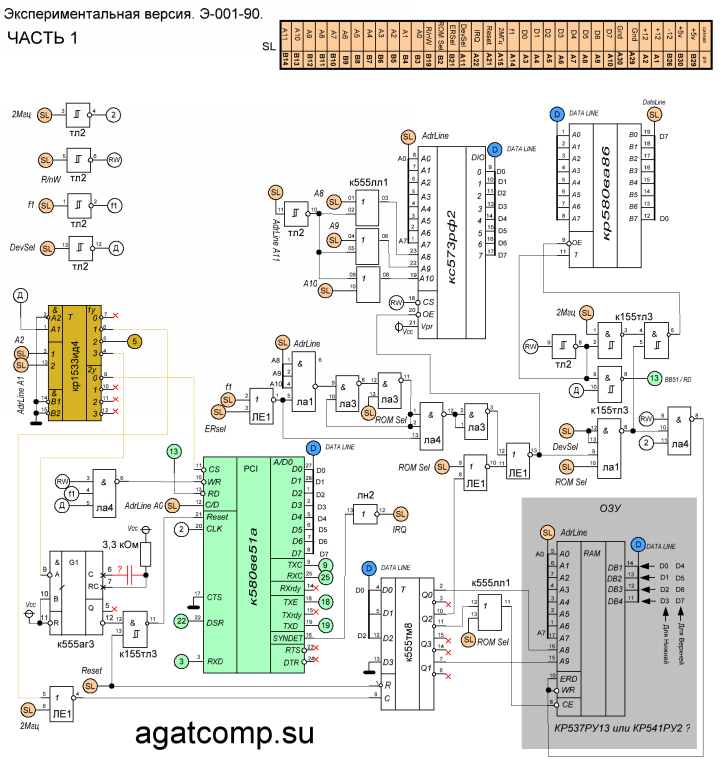

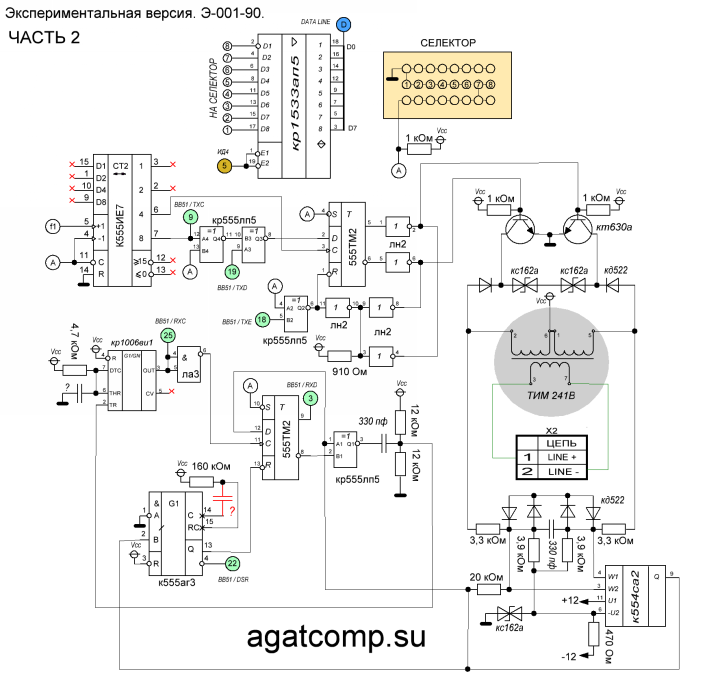

Экспериментальная версия. Э-001-90.

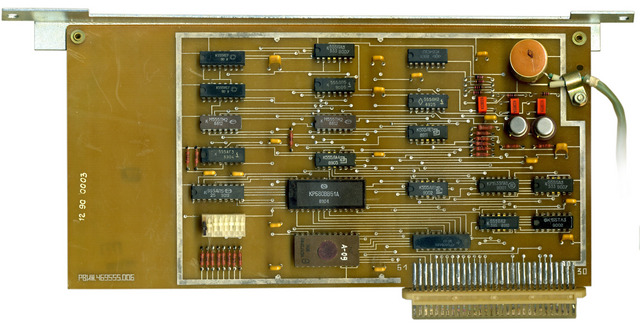

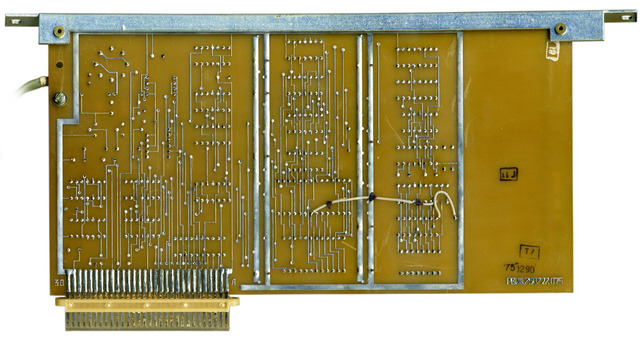

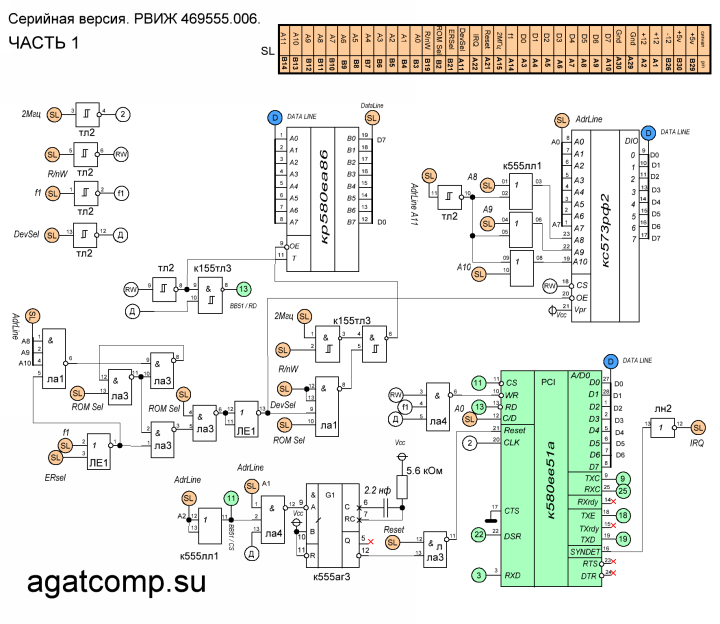

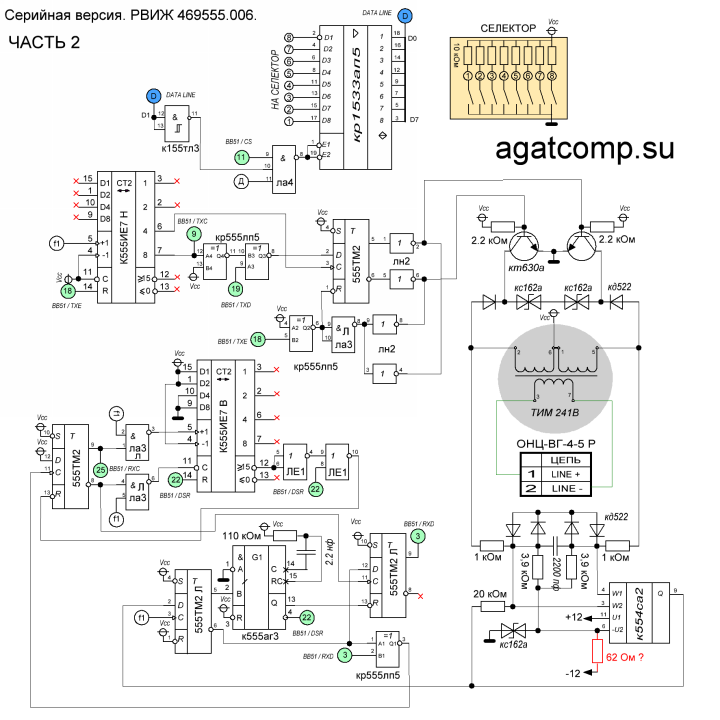

Серийная версия. РВИЖ 469555.006. Комплектовалась шнуром длинной 2 метра с разъемом ОНЦ-ВГ-4-5-Р.

См.также фотошаблон РВИЖ 758727.025 серийной версии платы.

* * *

Этот контроллер в мире PC назвали бы просто "сетевой картой". Причем наличествует ПЗУ удалённой загрузки. Изначально он разрабатывался для работы с коаксиалом, но в серию пошел вариант явно заточен под витую пару, причем, похоже, что даже в этом случае хабы агатовской сети не требовались. В отличие от Ethernet по витой паре, здесь использовалась только одна пара проводов для обоих направлений. Так что дуплекс не предполагался. Да и скорость была весьма невысокой. Но тем не менее, сеть допускала топологию "шина", что позволяло иметь одну пару проводов на весь класс машин. Допускался как адресный, так и широковещательный режим обмена. Имелась гальваническая развязка.

Аппаратно состоит из приёмопередатчика кр580вв51, схемы дополнительного кодирования/декодирования данных, магистрального формирователя сигнала (силовые каскады + гальваническая развязка + входной формирователь) и шинного интерфейса Агата. Схема кодирования формирует Манчестерский код (каждый бит передается как два бита, один из которых просто равен кодируемому биту, а второй - его инверсии). Поскольку Манчестерский код является самосинхронизирующимся, декодер во время приёма вылавливает из этого кода синхронизацию для ВВ51.

Скорость обмена -- 62500 бод/сек.

Контроллер использует три адресных пространства:

C0n0..C0nF

Cm00..CmFF

C800..CFFF

где n - номер слота + 8, m - номер слота.

ПЗУ драйвера отображается так:

- старшая страница всегда видна на Cm00..CmFF;

- после обращения к старшей странице включается отображение остальных страниц на C800..CEFF, после обращения к любому адресу CF00..CFFF отображение C800..CEFF отключается (поэтому по CF00..CFFF в любом случае читается мусор);

- также и после общесистемного RESET - C800..CEFF отключается.

Регистры управления: C0n0, C0n2, C0n8, C0nA - регистр данных ВВ51 (бит A0 напрямую подключен к 12 выводу ВВ51, дальше смотрим справочник); C0n1, C0n3, C0n9, C0nB - регистр управления ВВ51; C0n4, C0n5, C0nC, C0nD - чтение регистра сетевого адреса контроллера (устанавливается джамперами на плате, что-то вроде MAC-адреса); C0n6, C0n7, C0nE, C0nF - любая операция приводит к генерации сигнала RESET для ВВ51. Причем сигнал удерживается некоторое время, превышающее несколько тактов ЦПУ. На экспериментальной плате: C0n0, C0n8 - регистр данных ВВ51; C0n1, C0n9 - регистр управления ВВ51; C0n2, C0n3, C0nA, C0nB - регистр выбора страниц ОЗУ; C0n4, C0n5, C0nC, C0nD - чтение регистра сетевого адреса контроллера; C0n6, C0n7, C0nE, C0nF - сброс ВВ51.

Вероятно, ВВ51 штатно работает в т.н. "синхронном" режиме (во всяком случае на приём), при этом используется аппаратная фича ВВ51-й, позволяющая параллелить несколько приёмников на общей магистрали (микросхема будет слушать канал, но регистр данных будет заполнятся только после появления в канале специального кода - адреса. Причем отличить этот код от обычного байта с таким же значением микросхема не может, это возлагается на более высокоуровеный протокол).

Модуль также может генерировать прерывание IRQ, оно идёт через инвертор от вывода SYND/BD (лапка 16). Вроде бы в штатном режиме возникать будет при проскакивании в канале кода адреса, но вообще-то лапка многофункциональная и к тому же двунаправленная, так что ...

... читайте описание ВВ51 ! Самое простое (и не полное) есть у Мымрина, более подробное было где-то в "Микропроцессорных средствах и системах", ну а самое-самое, наверное - если найти описание исходного импортного аналога.

Кстати, у меня есть следующая заметка: ВВ51 отличается от ИК51: "Сброс D1 RxRDY слова состояния у ИК51 просиходит при чтении из любого регистра, а у ВВ51 только при чтении из регистра данных".

* * *

В 1988 году, в журнале "Микропроцессорные средства и системы", авторы опубликовали статью Контроллер локальной сети с планами по устройству.

Но, в отличие от этой статьи, в реальных контроллерах не реализована схема обнаружения конфликтов передачи, кроме того, магистраль сделана симметричной.

В экспериментальной версии, видимо, попытались упростить ту часть платы, которая отвечает за прием. В результате выкинули одну К555ТМ2, счетчик К555ИЕ7 и К555ЛА3, которая им управляла. На счетчике фактически был сделан одновибратор, в экспериментальной версии вместо него поставили настоящий одновибратор КР1006ВИ1.

Решение спорное. Потому что в схеме на счетчике задержка определяется тактовой частотой и, по сути, стабилизирована кварцевым резонатором. А схема на КР1006ВИ1 использует резистор и конденсатор для формирования задержки. Реальные резисторы и конденсаторы никогда не бывают того номинала, который на них написан. Они всегда немного отличаются. Кроме того, и сопротивление и емкость зависят от температуры. А следовательно и задержка. Так что схему на КР1006ВИ1 надо подстраивать, а в процессе работы задержка вообще может "уплыть". Видимо, осознав это, в серийной версии вернулись к той схеме, которая есть в статье.

Теперь, что касается КР1533ТМ8 и ОЗУ. ТМ8 используется для управления ОЗУ. Разряды D0 и D2 позволяют выбрать, какая часть ОЗУ будет видна при обращении по адресам CX00 - CXFF. Разряд D1 управляет тем, что сейчас используется: ОЗУ или ПЗУ. Схема построена так, что можно использовать либо ОЗУ, либо ПЗУ. Одновременно их использовать нельзя. Наиболее вероятная причина, почему так было сделано - отладка кода загрузочного ПЗУ. То есть, разработчики загружали код начальной загрузки в ОЗУ и отлаживали его. Думаю, это было намного удобнее, чем по поводу каждой найденной баги стирать старое ПЗУ и записывать новое. К тому же, в теории, можно было прямо не выключая машины поправить багу и продолжить отладку.

В серийной версии это было уже не нужно, код был отлажен и записан в ПЗУ, поэтому выкинули и ТМ8 и место для установки ОЗУ. Кроме того, упростился дешифратор адресов. В серийной версии его собрали на нескольких логических элементах и выкинули КР1533ИД4.

Кстати, в экспериментальной версии забавная ошибка: на КР580ВВ51А сигнал выборки подается при любом значении на шине адреса, у которого разряды A2 и A1 равны 0. Но, поскольку у ВВ51 входы чтения и записи отдельные и они формируются корректно, то никакого вреда от невпопад приходящей выборки нет.

См. также обсуждение контроллера сети на нашем форуме.